# Design and Implementation of 11,13 and 21-Level Inverter Configurations for Micro Grid Applications

V Kumar Reddy Majji<sup>1</sup>, D Tata Rao<sup>2</sup>, U P Kumar Chaturvedula<sup>3</sup>

<sup>1</sup>Assistant Professor, Department of Electrical and Electronics Engineering, Aditya College of Engineering, Surampalem, AP, India,

<sup>2</sup>Associate Professor, Department of Electrical and Electronics Engineering, Aditya College of Engineering, Surampalem, AP, India,

<sup>3</sup>Associate Professor, Department of Electrical and Electronics Engineering, Aditya College of Engineering, Surampalem, AP, India,

### Abstract:

The Renewable Energy Sources (RES) are the primary source of energy because of reduction in fossil fuels day to day. The primary resource in all available non-conventional energy sources is solar energy. Solar energy is obtained normally from Photo Voltaic (PV) cells. In PV cells a photo diode is used which converts the sun irradiation into DC voltage, which is normally a low value, so this is not sufficient to run the electrical loads which are connected to the micro grids. To avoid this problem, a novel boost converter is needed to improve the voltage profile, but it has a problem of high ripple content in voltage profile, which is not preferable for giving as i/p to the Inverter. Normally inverter will take constant DC as an i/p and convert into Alternating Current (AC) voltage. To avoid the above-described ripple, connect problem of boost converter, a novel hybrid Pulse Width Modulation (PWM) DC -DC converter is presented in this paper along with a SPWM inverter circuit which finds its applications in micro grids. The distinctive topologies of 13 and 21 level inverter have been analyzed with reduced number of switches also discussed in this paper. In traditional topologies a greater number of switches are required, and it can be decreased by planning the diverse topologies. The current distinctive topology is described and compared with the conventional configurations and the corresponding results are presented. With this it can be observed that the proposed topology gives the better outcomes. This can be utilized as a part of various micro grid inverter applications.

**Keywords:**Renewable Energy Sources (RES), Photo Voltaic (PV), Total Harmonic Distortion (THD), Pulse Width Modulation (PWM), Cascaded H-Bridge (CHB), Input (i/p), Output (o/p).

### 1.Introduction:

In current days, main role in power generation is with Renewable Energy Sources (RES) because of reduction in the fossil fuels normally acts as the main component of all readily available non-conventional energy sources. Energy is an essential factor for the functioning and economic development of the industrialized world. Energy management has become critical factor for our successive economic prosperity. The energy consumption process frequently needs either DC-AC conversion or AC-DC conversion. The DC-AC conversion finds its major application in uninterrupted power supply (UPS) and renewable energy (RES). In order to supply during power outages, most UPS systems use batteries, usually lead acid, as storage mechanism. The battery is supposed to provide the backup in the absence of the grid supply. However, the voltage provided by the battery alone may not be enough to provide the backup. At first, the battery o/p power which is DC needs to be

converted to AC with the help of an inverter. Apparently, the o/p of inverter needs to be step up with the help of step-up transformer to achieve an o/p of 220V, 50Hz [1]. An alternative approach to the same process is by using a power electronic converter called DC-DC boost converter. The boost converters are used in many applications, including photovoltaic systems, UPS, and fuel cell (FC) systems [1]. The standard DC-DC boost converter cannot provide a high gain. As it has been studied in the literature, when the voltage gain is high the efficiency of boost converter reduces. The reason being the losses in the intrinsic resistors of the converter increase when the duty cycle increases, this compromises the performance of the converter [2]-[3]. To overcome this limitation, high gain converter can be used to achieve higher gain [4]-[5]. AC o/p can be achieved with the help of inverter. Also, DC-AC conversion finds its application in RES systems. In such applications like solar photo voltaic (PV) systems, the DC o/p power from PV needs to be converted to AC power [6] & [7]. An Inverter circuit is used in cascade with a novel Pulse Width Modulation (PWM) DC-DC hybrid converter [3]&[8]. This cutting-edge PWM DC-DC hybrid converter is primarily utilized to enhance the PV cell voltage profile and reach the necessary i/p voltage level for an Inverter circuit that We have presented single phase 13 and 21-level MLIs in this article, Consider if 's 'number dc i/ps then generalized formula for number of level is 2S+1. The 21-levels of o/p through 10 H-cells this use power for micro grid applications.

# 2.11-Level CHB block diagram Multi level Inverter topology:

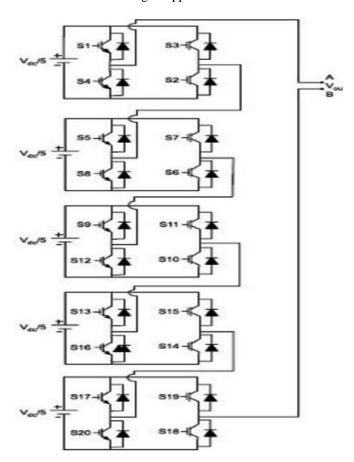

From the below topology it can be confirmed that with an increase in level of voltage the required number of switches is increasing which also increases the switching losses, cost and complexity of the circuit and algorithm for controlling the switches. To avoid the above drawbacks, it is proposed to see a novel inverter topology with a reduced number of switches for micro grid applications

Fig.1 Schematic diagram for a 11-level CHB Inverter Topology

| <br> |  |  |

|------|--|--|

|      |  |  |

|      |  |  |

| Voltage<br>Level     | Swi   | Switching Operation |                       |                |            |                       |            |            |                |                 |     |                 |                 |     |                 |                 |                 |     |     |                 |

|----------------------|-------|---------------------|-----------------------|----------------|------------|-----------------------|------------|------------|----------------|-----------------|-----|-----------------|-----------------|-----|-----------------|-----------------|-----------------|-----|-----|-----------------|

|                      | $S_1$ | $S_2$               | <b>S</b> <sub>3</sub> | S <sub>4</sub> | <b>S</b> 5 | <b>S</b> <sub>6</sub> | <b>S</b> 7 | <b>S</b> 8 | S <sub>9</sub> | S <sub>10</sub> | S11 | S <sub>12</sub> | S <sub>13</sub> | S14 | S <sub>15</sub> | S <sub>16</sub> | S <sub>17</sub> | S18 | S19 | S <sub>20</sub> |

| 0                    | 0     | 1                   | 0                     | 1              | 0          | 1                     | 0          | 1          | 0              | 1               | 0   | 1               | 0               | 1   | 0               | 1               | 0               | 1   | 0   | 1               |

| V <sub>dc</sub> /5   | 1     | 1                   | 0                     | 0              | 0          | 0                     | 0          | 0          | 0              | 0               | 0   | 0               | 0               | 0   | 0               | 0               | 0               | 0   | 0   | 0               |

| $2V_{dc}/5$          | 0     | 0                   | 0                     | 0              | 1          | 1                     | 0          | 0          | 0              | 0               | 0   | 0               | 0               | 0   | 0               | 0               | 0               | 0   | 0   | 0               |

| $3V_{dc}/2$          | 1     | 1                   | 0                     | 0              | 1          | 1                     | 0          | 0          | 1              | 1               | 0   | 0               | 0               | 0   | 0               | 0               | 0               | 0   | 0   | 0               |

| 4V <sub>dc</sub> /5  | 1     | 1                   | 0                     | 0              | 1          | 1                     | 0          | 0          | 1              | 1               | 0   | 0               | 1               | 1   | 0               | 0               | 0               | 0   | 0   | 0               |

| $V_{dc}$             | 1     | 1                   | 0                     | 0              | 1          | 1                     | 0          | 0          | 1              | 1               | 0   | 0               | 1               | 1   | 0               | 0               | 1               | 1   | 0   | 0               |

| -V <sub>dc</sub> /5  | 0     | 0                   | 1                     | 1              | 0          | 0                     | 0          | 0          | 0              | 0               | 0   | 0               | 0               | 0   | 0               | 0               | 0               | 0   | 0   | 0               |

| -2V <sub>dc</sub> /5 | 0     | 0                   | 1                     | 1              | 0          | 0                     | 1          | 1          | 0              | 0               | 0   | 0               | 0               | 0   | 0               | 0               | 0               | 0   | 0   | 0               |

| -3V <sub>dc</sub> /5 | 0     | 0                   | 1                     | 1              | 0          | 0                     | 1          | 1          | 0              | 0               | 1   | 1               | 0               | 0   | 0               | 0               | 0               | 0   | 0   | 0               |

| -4V <sub>dc</sub> /5 | 0     | 0                   | 1                     | 1              | 0          | 0                     | 1          | 1          | 0              | 0               | 1   | 1               | 0               | 0   | 1               | 1               | 0               | 0   | 0   | 0               |

| -V <sub>dc</sub>     | 0     | 0                   | 1                     | 1              | 0          | 0                     | 1          | 1          | 0              | 0               | 1   | 1               | 0               | 0   | 0               | 0               | 0               | 0   | 1   | 1               |

Table 1: Switching of a 11-level CHB converter

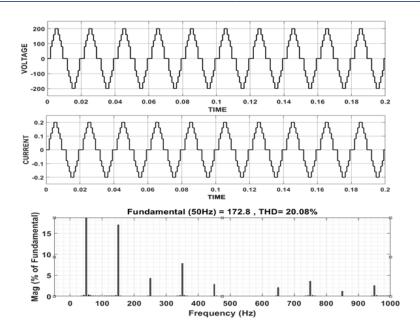

# 3. MATLAB/Simulink model for 11-level CHB inverter fed to R-load:

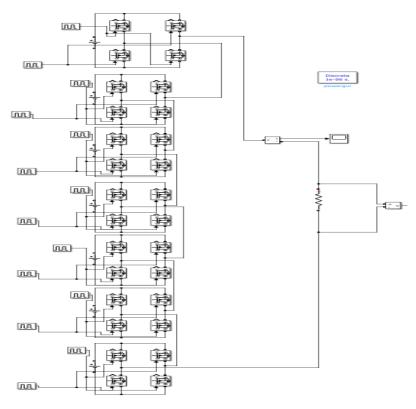

11-level topology for a CHB inverter is shown in Figure 1. And the corresponding MATLAB/Simulink model is shown in Figure 2. In this circuit we are using a total of 20 switches to get the 11-level o/p wave form as shown in figure 3.

Fig.2 MATLAB/Simulink model for a 11-level CHB inverter

Fig.3 Voltage, current & FFT wave form of 11-level CHB inverter

# 4. 13-Level CHB block diagram Multi level Inverter topology:

The below Figure 4 represents the circuit topology for 13-level CHB inverter and also the respective switching sequence is given in Table 2.

Fig.4 Schematic diagram for a 13-level CHB Inverter

| Volta                |                | _              |                |                |                |                |                |                |                | Sw              | itel           | ning            | Seq             | uen             | ice            |                | _              | _              |                |                |                |                |                | _              |

|----------------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|-----------------|----------------|-----------------|-----------------|-----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

| ge<br>Level          | S <sub>1</sub> | S <sub>2</sub> | S <sub>3</sub> | S <sub>4</sub> | S <sub>5</sub> | S <sub>6</sub> | S <sub>7</sub> | S <sub>8</sub> | S <sub>9</sub> | S <sub>10</sub> | S <sub>1</sub> | S <sub>12</sub> | S <sub>13</sub> | S <sub>14</sub> | S <sub>1</sub> | S <sub>2</sub> |

| 0                    | 1              | 1              | 0              | 1              | 0              | 1              | 0              | 1              | 0              | 1               | 0              | 1               | 0               | 1               | 0              | 1              | 0              | 1              | 0              | 1              | 0              | 1              | 0              | 1              |

| $V_{dc}/6$           | 1              | 0              | 0              | 1              | 0              | 1              | 0              | 1              | 0              | 1               | 0              | 1               | 0               | 1               | 0              | 1              | 0              | 1              | 0              | 1              | 0              | 1              | 0              | 1              |

| $V_{dc}/3$           | 1              | 0              | 0              | 1              | 1              | 0              | 0              | 1              | 0              | 1               | 0              | 1               | 0               | 1               | 0              | 1              | 0              | 1              | 0              | 1              | 0              | 1              | 0              | 1              |

| $V_{dc}/2$           | 1              | 0              | 0              | 1              | 1              | 0              | 0              | 1              | 1              | 0               | 0              | 1               | 0               | 1               | 0              | 1              | 0              | 1              | 0              | 1              | 0              | 1              | 0              | 1              |

| $2V_{dc}/3$          | 1              | 0              | 0              | 1              | 1              | 0              | 0              | 1              | 1              | 0               | 0              | 1               | 1               | 0               | 0              | 1              | 0              | 1              | 0              | 1              | 0              | 1              | 0              | 1              |

| $5V_{dc}/6$          | 1              | 0              | 0              | 1              | 1              | 0              | 0              | 1              | 1              | 0               | 0              | 1               | 1               | 0               | 0              | 1              | 1              | 0              | 0              | 1              | 0              | 1              | 0              | 1              |

| $V_{\text{dc}}$      | 1              | 0              | 0              | 1              | 1              | 0              | 0              | 1              | 1              | 0               | 0              | 1               | 1               | 0               | 0              | 1              | 1              | 0              | 0              | 1              | 1              | 0              | 0              | 1              |

| $-V_{dc}/6$          | 0              | 1              | 1              | 0              | 1              | 0              | 1              | 0              | 1              | 0               | 1              | 0               | 1               | 0               | 1              | 0              | 1              | 0              | 1              | 0              | 1              | 0              | 1              | 0              |

| $-V_{dc}/3$          | 0              | 1              | 1              | 0              | 0              | 1              | 1              | 0              | 1              | 0               | 1              | 0               | 1               | 0               | 1              | 0              | 1              | 0              | 1              | 0              | 1              | 0              | 1              | 0              |

| $-V_{dc}/2$          | 0              | 1              | 1              | 0              | 0              | 1              | 1              | 0              | 0              | 1               | 1              | 0               | 1               | 0               | 1              | 0              | 1              | 0              | 1              | 0              | 1              | 0              | 1              | 0              |

| $-2V_{dc}/3$         | 0              | 1              | 1              | 0              | 0              | 1              | 1              | 0              | 0              | 1               | 1              | 0               | 0               | 1               | 1              | 0              | 1              | 0              | 1              | 0              | 1              | 0              | 1              | 0              |

| -5V <sub>dc</sub> /6 | 0              | 1              | 1              | 0              | 0              | 1              | 1              | 0              | 0              | 1               | 1              | 0               | 0               | 1               | 1              | 0              | 0              | 1              | 1              | 0              | 1              | 0              | 1              | 0              |

|                      | <u> </u>       | ١.             |                | -              | -              | ٠.             | <del>.</del>   | -              | -              | <u> </u>        |                | -               | -               | <u> </u>        | ٠.             | <del>-</del>   | -              |                |                | -              | -              | <del> </del>   | <del>-</del>   | $\vdash$       |

Table 2: Switching of a 13-level CHB Inverter

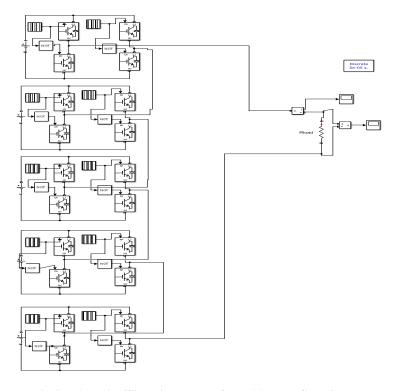

## 5. MATLAB/Simulink model for 13-level CHB inverter fed to R-load.

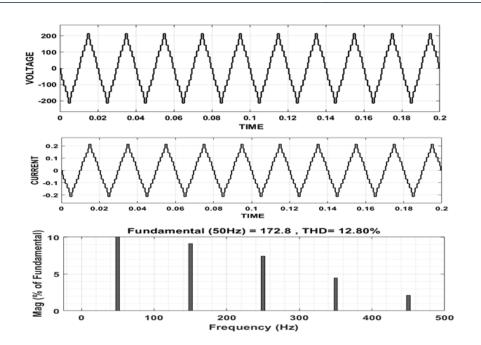

Mat lab/Simulink model for a 13- level inverter topology for a CHB inverter is shown in figure 5. In this circuit we are using a total of 24 switches are used to get 13-level single phase o/p voltage and current and THD wave form in figure 6.

Fig.5 MATLAB/Simulink model for a 13-level inverter

Fig.6 Voltage, current & FFT wave form of 13-level CHB inverter

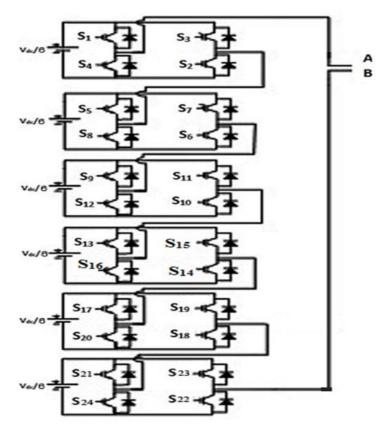

# 5. 21 -Level CHB Multi level Inverter topology:

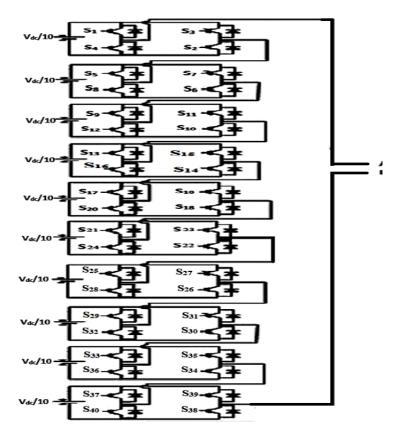

The block diagram of Conventional Single Phase 21- level CHB Multilevel Inverter is shown in Figure 7 .and also the respective switching operation is also mentioned below.

Fig.7 Single Phase 21-level CHBM Inverter

Table 4 gives 21-level CHB Inverter with 21 different voltage o/p levels with an appropriate control scheme of the switches. The sum of different individual H-bridge inverter o/p connected in series is synthesized to get the final sinusoidal o/p voltage for the multilevel inverter.

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 0 10 20 30 40 50 60 70 80 90 100 90 80 70 60 50 40 30 20 10 0 -10 -20 -30 -40 -50 -60 -70 -80 -90 -100 -90 -80 -70 -60 -50 -40 -30 -20 -10 11 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 0 1 1 1 0 1 1 0 0 1 0 1 1 0 1 1 1 0 1 1 1 1 1 0 0 0 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 9 70 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 0 11 91 1 1 1 1 1 1 1 1 1 0 13 11 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 1 0 0 0 0 Û 0 0 14 12 0 0 0 1 0 0 0 1 1 1 0 0 0 0 0 0 0 0 0 15 13 1 1 1 1 1 1 1 1 1 1 1 1 0 16 14 1 1 1 1 0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1 17 15 0 0 0 0 0 0 0 0 0 0 00000000000000001111 1

Table 4: Switching of a 21-level CHB Inverter

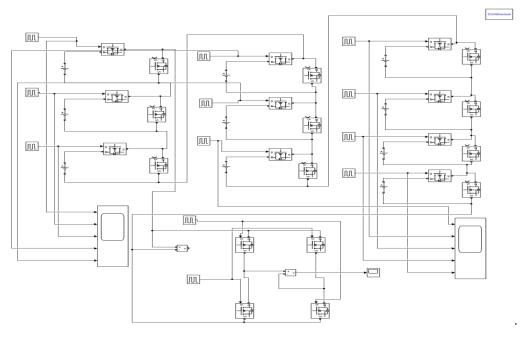

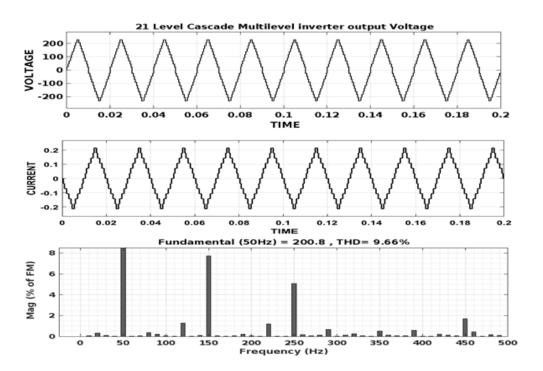

### 6. MATLAB /Simulink model for A Novel PV based 21-level CHB Inverter.

The 21-level topology configuration of a CHB is shown below. In this circuit we are using a total of 40 switches to get 21-level single phase o/p voltage and current and THD wave form in figure 9

Fig.8 MATLAB/Simulink model of 21-level CHB inverter

Fig.9 Voltage, current & FFT wave form of 21-level CHB inverter

| S.No | Parameters              | CHB-11 level | CHB-13 level | CHB-21 level |

|------|-------------------------|--------------|--------------|--------------|

| 1    | No.of switches          | 20           | 28           | 40           |

| 2    | No.of dc<br>Supply volt | 5            | 7            | 10           |

| 3    | Load resistence         | 1k           | 1k           | 1K           |

| 4    | In put volt             | 210          | 250          | 240          |

| 5    | O/p volt                | 200          | 209          | 223          |

| 6    | O/p current             | 0.200        | 0.209        | 0.223        |

| 7    | Total THD%              | 20.08        | 12.80        | 9.66         |

Table 5: Comparison of 11, 13 and 21-level Inverter

### **Conclusion:**

In this paper we have compared the conventional cascaded 11,13 and 21 level inverters by using a closed loop intelligent control algorithm to optimize the switching angle. The designing and implementation of further levels may reduce the THD to a lesser value and there by overcome the existing problems of multilevel inverters. Thus, from the above presented results, it is concluded that, the present control algorithm configuration gives low THD and improved efficiency with a reduced number of switches. So, these models are highly suitable and recommended for micro-grid applications because it require an efficient converter with low cost and less design complexity.

## **AUTHOR'S CONTRIBUTIONS:**

Author1: Conceptualization, methodology, validation.

# Tuijin Jishu/Journal of Propulsion Technology

ISSN: 1001-4055 Vol. 45 No. 1 (2024)

Author2: Supervision, visualization, validation.

Author3: Software, methodology and review.

### **References:**

- [1] Sandeep, N., and Udaykumar R. Yaragatti. "Design and implementation of active neutral-point-clamped nine-level reduced device count inverter: an application to grid integrated renewable energy sources." IET Power Electronics 11, no. 1 (2017): 82-91.

- [2] Reddi, Naresh Kumar, Manoj R. Ramteke, Hiralal M. Suryawanshi, KoteswararaoKothapalli, and Snehal P. Gawande. "An isolated multi-input ZCS DC–DC front-end-converter based multilevel inverter for the integration of renewable energy sources." IEEE Transactions on Industry Applications 54, no. 1 (2017): 494-504.

- [3] Agrawal, Rekha, and Shailendra Jain. "Multilevel inverter for interfacing renewable energy sources with low/medium-and high-voltage grids." IET Renewable Power Generation 11, no.14 (2017): 1822-1831.

- [4] Dasgupta, Souvik, Shankar Narayan Mohan, Sanjib Kumar Sahoo, and Sanjib Kumar Panda. application of four-switch-based three-phase grid-connected inverter to connect renewable energy source to a generalized unbalanced microgrid system." IEEE Transactions on Industrial Electronics 60, no. 3 (2012): 1204-1215.

- [5] Sahan, Benjamin, Samuel V. Araujo, Christian Nöding, and Peter Zacharias. "Comparative evaluation of three-phase current source inverters for grid interfacing of distributed and renewable energy systems." IEEE Transactions on Power Electronics 26, no. 8 (2010): 2304-2318.

- [6] Jain, Sachin, and Venu Sonti. "A highly efficient and reliable inverter configuration based cascaded multilevel inverter for PV systems." IEEE transactions on industrial electronics 64, no. 4 (2016): 2865-2875

- [7] Hsieh, Cheng-Han, Tsorng-Juu Liang, Shih-Ming Chen, and Shih-Wen Tsai. "Design and implementation of a novel multilevel DC–AC inverter." IEEE Transactions on Industry Applications 52, no. 3 (2016): 2436-2443.

# Tuijin Jishu/Journal of Propulsion Technology

ISSN: 1001-4055 Vol. 45 No. 1 (2024)

V Kumar Reddy MAJJI working as Assistant Professor in Department of Electrical and Electronics Engineering in Aditya College of Engineering, surampalem, AP, India. He has total 7years of Experience as an Assistant professor. His Research areas includes Power Electronics, Electrical Drives and Hybrid Electrical Vehicles. He has published various articles on multilevel inverters, He is a life member of ISTE, IETE, IAENG.

D Tata Rao working as Associate Professor in Department of Electrical and Electronics Engineering in Aditya College of Engineering, surampalem, AP, India. His Research areas includes Power Systems, Electrical Vehicles, He have published various articles in Electrical Engineering, He has 2 years of Industrial Experience and 20 years teaching experience. He is a life member of ISTE, IETE, IAENG.

U P Kumar Chaturvedula is designated as Associate Professor in the Department of Electrical and Electronics Engineering at Aditya College of Engineering, Surampalem, A.P, India. His research areas include smart grids, power system optimization and electrical power distribution systems. He has teaching experience of 20years. He is a life member of ISTE, IETE, IAENG.